ASML prévoit une large utilisation de la technologie High‑NA EUV dès l’année prochaine pour fabriquer des puces avec des transistors d’une taille de 1,4 nm et moins.

Résumé

La nouvelle étape de miniaturisation des circuits intégrés exige la transition vers des méthodes de lithographie plus avancées. Au cours des deux prochaines années, le secteur doit lancer la production de puces utilisant du matériel de classe High‑NA EUV, permettant d’atteindre des tailles jusqu’à 8 nm en un seul passage et ouvrant la voie à des processus technologiques de 1,4 nm et moins de 10 nm (DRAM).

1. Capacités technologiques du High‑NA EUV

Paramètre | Valeur

---|---

Aperture numérique (NA) | 0,55

Taille minimale en un passage | ≤ 8 nm

Processus possibles | 1,4 nm (circuit intégré), < 10 nm (DRAM)

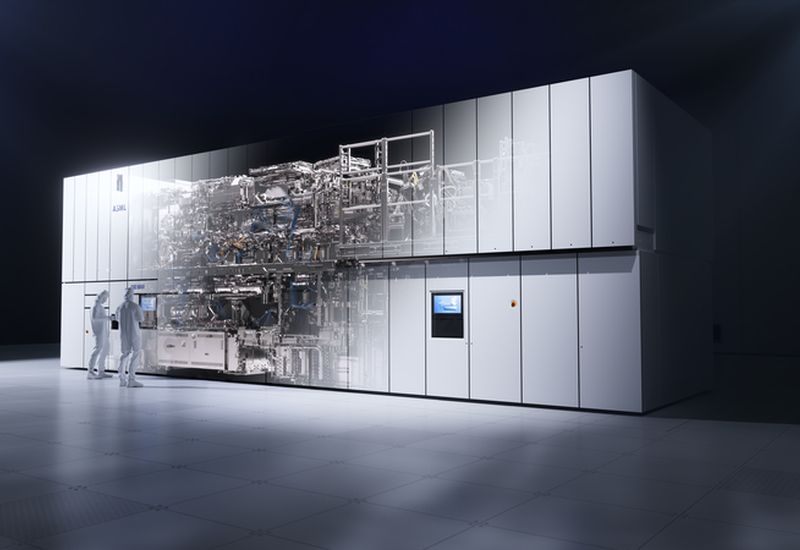

Ces caractéristiques rendent le matériel ASML Twinscan EXE:5200B et des solutions similaires critiques pour les futures technologies microélectroniques.

2. Acteurs clés

Entreprise | Statut de mise en œuvre | Commentaire

---|---|---

ASML | Fabricant du High‑NA EUV | Premiers clients : Intel, Samsung, SK Hynix

TSMC | Pas prêt à l’usage massif | Coût d’une unité – 380 mln USD ; plan de retrait des puces 1,4 nm

Intel | En décembre 2023 a introduit le Twinscan EXE:5200B | Préparation au lancement de la technologie 14A et du matériel associé

Samsung Electronics | A reçu son premier scanner en décembre 2023; second – ce semestre | Prévoyait de l’utiliser pour Exynos 2600 (2 nm) et les futurs processeurs Tesla

SK Hynix | Maîtrise le High‑NA EUV depuis septembre 2023 | Utilise déjà la lithographie EUV standard en DRAM (10 nm), prévoit d’employer au moins cinq couches EUV pour la 6ᵉ génération

Micron Technology | Pas encore de dates définies | Plans possibles pour le High‑NA EUV

Rapidus (Japon) | Maîtrise la technologie 2 nm ; vise 1,4 nm en 2029 | En 2027 devrait lancer la production massive de puces 2 nm à Hokkaido

3. Aspects économiques

* Le coût du matériel – une unité High‑NA EUV coûte environ 380 mln USD.

* Passer à un équipement plus cher augmente le coût de revient, ce qui se répercute finalement sur les consommateurs.

* Les grands producteurs (TSMC, Rapidus) font preuve de prudence et prévoient une mise en œuvre progressive.

4. Délais attendus

Les nouveaux scanners lithographiques ASML destinés à la production massive de semi-conducteurs avancés commenceront à être utilisés activement entre 2027 et 2028. D’ici là, les entreprises ajusteront progressivement leurs lignes de production, intégrant le High‑NA EUV dans leurs processus technologiques existants.

Conclusion

La transition vers le High‑NA EUV est une étape clé pour atteindre des tailles jusqu’à 1,4 nm et des DRAM plus compacts. Les principaux acteurs mondiaux ont déjà entamé les travaux préparatoires, mais l’adoption massive ne devrait se produire que dans quelques années en raison des coûts élevés et de la nécessité d’adapter les chaînes de production.

Asted Cloud

Asted Cloud

Commentaires (0)

Partagez votre avis — merci de rester courtois et dans le sujet.

Connectez-vous pour commenter